JUEGO DE TIRO A CANASTA CON INDICADOR DE PUNTOS

FASE 4:

IMPLEMENTACIÓN

1. COMPETENCIAS ESPECÍFICAS:

- Conocer el proceso de desarrollo de un proyecto con PIC.

- Aplicar todas las técnicas de programador conocidas hasta este momento.

- Aplicar estos conocimientos en la realización de un proyecto.

2. MARCO TEÓRICO:

Manejo de las interrupciones en un PIC:

Es decir, una interrupción es una técnica particular del PIC que permite: interceptar eventos externos de un programa en ejecución, interrumpiendo momentáneamente la operación del programa, controla el evento con una subrutina apropiada, y retorna para continuar con la ejecución del programa en el punto donde se produjo la interrupción.

La familia del PIC16F87x cuenta con hasta 14 fuentes de interrupcion, de las cuales algunas de ellas se habilitan por medio de diferentes registros de control:

- Las fuentes de interrupción se ven con INTCON

- La del convertidor A/D se encuentra en el registro PIE1, en este mismo registro está el bit del TIMER1 (TMRIE ,PIE1<0>) entre otros.

El registro INTCON cuenta con tres controles de interrupción cada uno derivado auna función específica:

- Interrupciones ocasionadas en la patilla RBO/INT

- Interrupciones ocasionadas por cambios de estado en las patillas RB7:RB4

- Interrupciones que tienen lugar por el desbordamiento del temporizador TMR0

- Interrupciones referidas al resto de los controles de periféricos y funciones especiales se encuentran en los registros PIR1, PIR2.

Tipos de Eventos y Bits de Habilitación:

En el registro INTCOIN solo se encuentran tres controles de interrupciones:

- Un cambio de estado sobre la línea RB0 ( pin de interrupción externa RB0/INT

- Desbordamiento de la cuenta del registro TMR0 ( TMR0 overflow interrupt )

- Un cambio de estado sobre una de las líneas de RB4 a RB7 ( PORTB change interrupts ).

Los cuales se describen a continuación

1. Interrupción de TMR0

- Si el temporizador TMR0 se ha desbordado, el flag de overflow (T0IF) del registro INTCON se habrá puesto a uno. Es evidente que previamente se habrán borrado todos los flags que pudieran ocasionar una interrupción, así se evitarán interrupciones recursivas. Para habilitar esta interrupción se debe poner en 1 el bit T0IE.

2. Interrupción externa por RBO/INT:

- Las transiciones de bajo a alto, o viceversa, de la patilla RB0/INT puede ocasionar una interrupción, el flanco que la producirá se elige con el bit INTEDG (OPTION_REG<6>). Cuando este bit se pone a uno, la interrupción tendrá lugar en la transición de cero a uno, por el contrario, el flanco de bajada ocasionará la interrupción cuando el bit se coloque a cero. En cuanto tenga lugar en la patilla RB0/INT el flanco elegido, el bit INTF (INTCON<1>) se pondrá a uno; el estado de los bits de interrupciones globales (GIE) e interrupción externa (INTE) determina si se atenderá o no la interrupción. Si están habilitadas y el microcontrolador se encuentra en reposo (Sleep) éste despertará.

3. Interrupción por cambio de estado en RB4:RB7:

- Además de la interrupción externa descrita, estos microcontroladores se disponen de otro modo de ocasionar una interrupción externa; cualquier cambio de estado que se produzca en las patillas RB7:RB4 también la ocasionará, para habilitarla, hay que poner a uno el flag de interrupciones.

- RBIE (INTCON<3>). Cualquier cambio de estado que haya en estas patillas hará que el bit RBIF (INTCON<0>) se ponga a uno y se produzca la interrupción. Para que el sistema pueda ocasionar una interrupción por cambios de estado en las patillas RB7:RB4 es necesario realizar algunas actuaciones previas que no son necesarias en otro tipo de interrupciones ya que el estado de estas cuatro patillas es comparado continuamente, en la fase Q1 del reloj, con el estado previo de los latch del puerto. Por consiguiente, antes de habilitar esta interrupción habrá que leer o escribir en él para que su contenido se quede almacenado en los latch; solamente los bits configurados como entradas se comparan y si son diferentes a los previamente almacenados pueden ocasionar una interrupción.

El resto de los controles de periféricos y funciones especiales se encuentran en los registros PIR1, PIR2 (Banderas) y PIE1, PIE2 (Mascaras). Una interrupción de cualquiera de estos eventos puede ser conseguida habilitando o deshabilitando independientemente los siguientes bits de los registro INTCON, PIR1 y, PIR2:

- INTE: Si este bit está en 1 habilitará la interrupción de cambio de estado sobre la línea RBO.

- TOIE: Si este bit está en 1 habilitará la interrupción de final de conteo del registro TMRO.

- RBIE: Si este bit está en 1 habilitará la interrupción de cambio de estado sobre una de las líneas de RB4 a RB7.

- EEIE: Si este bit está en 1 habilitará la interrupción de final de escritura sobre la EEPROM.

- PSPIE: Si este bit está en 1 habilitará la interrupción por lectura/escritura en el PSP.

- ADIE: Si este bit está en 1 habilitará la interrupción del convertidor A/D.

- RCIE: Si este bit está en 1 habilitará la interrupción por recepción en el USAR.

- TXIE: Si este bit está en 1 habilitará la interrupción de transmisión por el USAR.

- SSPIE: Si este bit está en 1 habilitará la interrupción del SSP.

- CCP1IE: Si este bit está en 1 habilitará la interrupción CCP1.

- TMR2IE: Si este bit está en 1 habilitará la interrupción por el desbordamiento de TMR2 emparejado a PR2.

- TMR1IE: Si este bit está en 1 habilitará la interrupción por desbordamiento de TMR1.

- CCP2IE: Si este bit está en 1 habilitará la interrupción de CCP2.

- BCLIE: Si este bit está en 1 habilitará la interrupción por colisión de bus SSP.

Vector de interrupción y control de interrupción:

Cualquier evento que sea habilitado, o se manifieste, el PIC interrumpe la ejecución del programa, almacena automáticamente en el STACK el valor actual del PROGRAM COUNTER y este pasa a ejecutar la instrucción presente en la dirección de memoria 0004H, denominada Interrupt Vector ( vector de interrupción ). Por lo tanto, desde este punto debemos colocar la llamada a la subrutina de control denominada Interrupt Handler (control de interrupción).

Bandera de Interrupción:

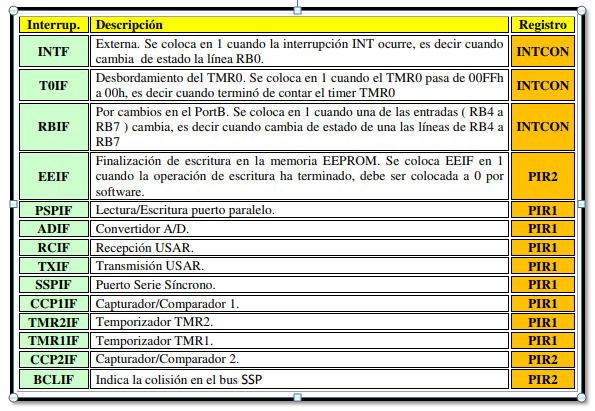

Dado que cualquier interrupción genera una llamada a la dirección 04H, en los registros INTCON, PIR1 y PIR2 está presente varias banderas que indican cuál evento es el que genera la interrupción, las cuales se describen a continuación:

Diagrama lógico de las interrupciones:

La lógica de activación de mascaras y banderas descrita arriba puede entenderse en términos del diagrama lógico mostrado en la siguiente figura. En este diagrama se muestran las 14 fuentes de interrupción de los microcontroladores de la familia PIC16F87x y se usan los nombres específicos de cada fuente de interrupción para sus respectivas banderas y mascaras de interrupción.

La siguiente tabla muestra las diferencias entre los dos modelos de 28 y 40 pines.

Vídeo del desarrollo

No hay comentarios:

Publicar un comentario